Discover and read the best of Twitter Threads about #fpga

Most recents (22)

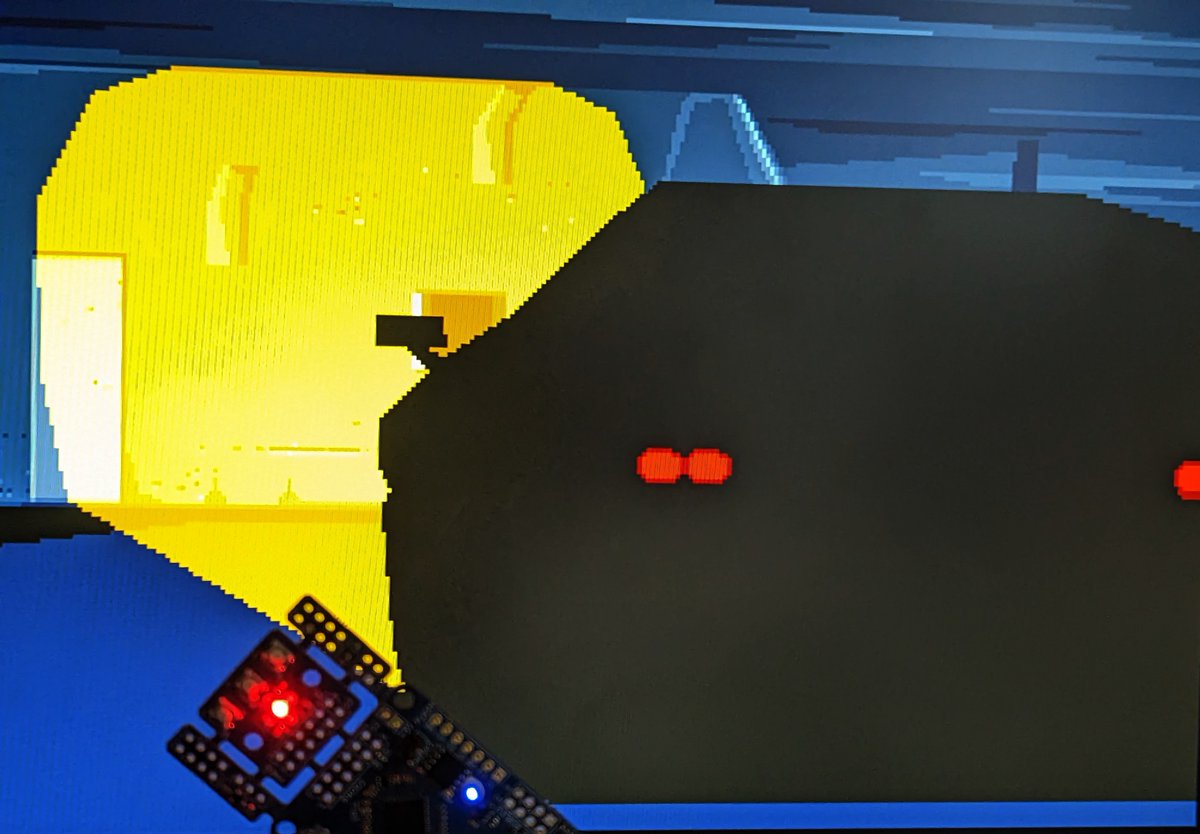

a5k: Another World on a chip! This is a hardware remake of the Another World VM and renderer (no traditional CPU), that fits on a UP5K #fpga (5K LUTs, 128KB SPRAM).

Thread! (1/n)

(Written in #Silice, running on @1bitsquared icebreaker + VGA PMOD, intro only, no audio)

Thread! (1/n)

(Written in #Silice, running on @1bitsquared icebreaker + VGA PMOD, intro only, no audio)

2/ Another World by @EricChahi was one of my favorite #Amiga500 games. It's a great game with beautiful polygon-based graphics. Its architecture is also fascinating: the whole game runs in a custom VM

As the game turned 31 I thought a hardware version would make a great present!

As the game turned 31 I thought a hardware version would make a great present!

3/ @fabynou has several great blog entries detailing the game inner workings, with links to additional resources including source code. I won't go into much details here so check it out for an in-depth overview!

fabiensanglard.net/another_world_…

fabiensanglard.net/another_world_…

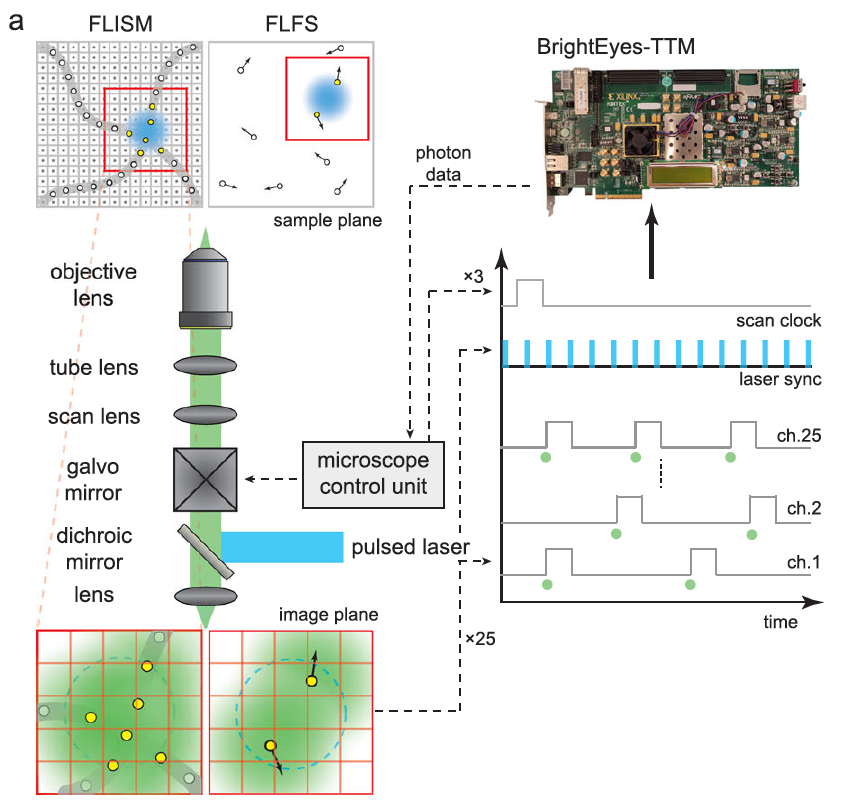

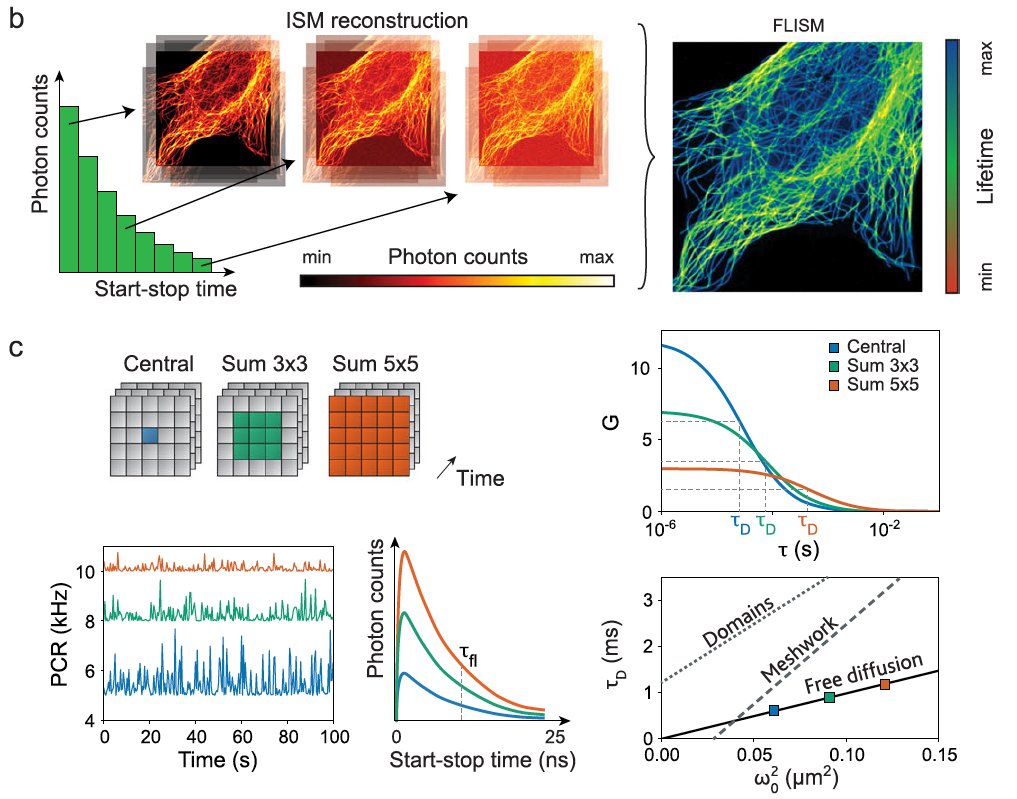

#quantum is here! Why not collect #fluorescence #photon-by-photon in your laser-scanning #microscope? We developed the #BrightEyes_TTM, an #opensource data acquisition system able to do it!

nature.com/articles/s4146…

@IITalk @ERC_Research @RNA_iit @MSCActions #BrightEyes_ERC

(1/5)

nature.com/articles/s4146…

@IITalk @ERC_Research @RNA_iit @MSCActions #BrightEyes_ERC

(1/5)

Our time-tagging #DAQ module can collect single-photon signals from 25 independent channels and reference signals from 3 channels. We showed how this module combined with a #SPAD array allows us to perform #FLISM and #FLFS. (2/5)

#imagescanningmicroscopy #fluorescence #lifetime

#imagescanningmicroscopy #fluorescence #lifetime

We characterized the #BrightEyes_TTM. We can reach a single-shot precision of 30 ps, 4 ns dead-time, and an "infinite" range in all channels, with a total flux of up to 125 MHz. (3/5)

#TCSPC #antibunching #quantum #microscopy #FPGA

#coding #LIDAR

#TCSPC #antibunching #quantum #microscopy #FPGA

#coding #LIDAR

1/ Introducing Cloud-ZK: A Toolkit for Developing Zero Knowledge Proof Acceleration in the Cloud 🥳

TL;DR

Today we #opensource a new way to accelerate ZK. Using #FPGA. In #AWS cloud. Easy. Accessible. Cheap.

Read on, or check out the blog

Thread 🧵👇

github.com/ingonyama-zk/c…

TL;DR

Today we #opensource a new way to accelerate ZK. Using #FPGA. In #AWS cloud. Easy. Accessible. Cheap.

Read on, or check out the blog

Thread 🧵👇

github.com/ingonyama-zk/c…

2/

Zero Knowledge (ZK) technology is a fundamental building block for decentralized computing.

Its two main applications are privacy-preserving computation and verifiable computation.

Blogpost: medium.com/@ingonyama/clo…

Zero Knowledge (ZK) technology is a fundamental building block for decentralized computing.

Its two main applications are privacy-preserving computation and verifiable computation.

Blogpost: medium.com/@ingonyama/clo…

3/

For specific types of ZK such as SNARK and STARK-based systems, additional properties include public verifiability, smaller proof sizes, and fast verification.

This makes these kinds of ZK perfect for use in blockchains for scalability and privacy purposes.

For specific types of ZK such as SNARK and STARK-based systems, additional properties include public verifiability, smaller proof sizes, and fast verification.

This makes these kinds of ZK perfect for use in blockchains for scalability and privacy purposes.

西門子電器 99% 中國貼牌 OEM

西門子半導體龍頭?我都唔係好知要搵搵料

哦咪 #FPGA 連帶 HDL/VHDL/EDA/Verilog etc.,我大學時(10年內)無西門子

DOD 最初 80s玩起,90s 開放俾民間用,Xinlix Honeywell Rockwell Texas Inst. 一早已有

簡單講電子產品發展咁快,大部分黎自於美帝武器系統

1

西門子半導體龍頭?我都唔係好知要搵搵料

哦咪 #FPGA 連帶 HDL/VHDL/EDA/Verilog etc.,我大學時(10年內)無西門子

DOD 最初 80s玩起,90s 開放俾民間用,Xinlix Honeywell Rockwell Texas Inst. 一早已有

簡單講電子產品發展咁快,大部分黎自於美帝武器系統

1

美國以外,最多既係英國

英國 Chord 同 Naim 更加用FPGA 黎造音響

至於 d 大工程,CLP 新 D1 D2 (Combined Cycle Gas Turbine) CCGT 我有份起,絕對唔係咩新科技,隨便數ABB GE 三菱 日立 Babcock Thales Schneider 間間都做到

好多時中標係商業同政治因素,鐵路亦係

2

#Engineering_pt_view

英國 Chord 同 Naim 更加用FPGA 黎造音響

至於 d 大工程,CLP 新 D1 D2 (Combined Cycle Gas Turbine) CCGT 我有份起,絕對唔係咩新科技,隨便數ABB GE 三菱 日立 Babcock Thales Schneider 間間都做到

好多時中標係商業同政治因素,鐵路亦係

2

#Engineering_pt_view

武器系統既話,我舉兩樣多國合作 project,Tonardo 同 EF-2000

德國既參與其實好少,最多既係英國,投產實用之後好多system upgrade 甚少係德國,而係英國做

法國中途退出另起爐灶

英法係德國之上

唯獨係潛艇,大部分機密唔公開,可能二戰 UBOAT 既關係都未定 (水面唔夠打先玩潛艇)

3

德國既參與其實好少,最多既係英國,投產實用之後好多system upgrade 甚少係德國,而係英國做

法國中途退出另起爐灶

英法係德國之上

唯獨係潛艇,大部分機密唔公開,可能二戰 UBOAT 既關係都未定 (水面唔夠打先玩潛艇)

3

Q5K: Quake level viewer in 5K LUTs on a low cost, low power ice40 up5k #fpga! Custom #GPU, @risc_v CPU and SOC, capable of rendering #Quake's level with lightmaps.

How? Thread 👇

(Written in #Silice, here running on the #mch2022 badge fpga)

How? Thread 👇

(Written in #Silice, here running on the #mch2022 badge fpga)

NetSec session is over today and dr. Matěj Bartík from Digiteq Automotive continues with his #industrial #talk on hardware data processing and various available products. @XilinxInc, #FPGA and #Zynq keywords at #PESW2022.

The afternoon part of #PESW2022 program was started by prof. Miloš Krstić from @waferffo - Machine Learning from hardware perspective in the keynote called "Reliability evaluation of general purpose and AI processing architectures"

@threadreaderapp unroll

#Highlights2021 for me: our #survey on efficient processing of #sparse and compressed tensors of #ML/#DNN models on #hardware accelerators published in @ProceedingsIEEE.

Paper: dx.doi.org/10.1109/JPROC.…

arXiv: arxiv.org/abs/2007.00864

RT/sharing appreciated. 🧵

Paper: dx.doi.org/10.1109/JPROC.…

arXiv: arxiv.org/abs/2007.00864

RT/sharing appreciated. 🧵

Context: Tensors of ML/DNN are compressed by leveraging #sparsity, #quantization, shape reduction. We summarize several such sources of sparsity & compression (§3). Sparsity is induced in structure while pruning & it is unstructured inherently for various applications or sources.

Likewise, leveraging value similarity or approximate operations could yield irregularity in processing. Also, techniques for size-reduction make tensors asymmetric-shaped. Hence, special mechanisms can be required for efficient processing of sparse and irregular computations.

💥Day 1: Doom iCEBreaker Edition

An iCE40UP #FPGA is tiny, with just 5000 logic cells, but that didn't stop Sylvain Munaut from running Doom. The design uses a @1bitsquared iCEBreaker board with added SPI ram.

Watch:

Source: github.com/smunaut/doom_r…

An iCE40UP #FPGA is tiny, with just 5000 logic cells, but that didn't stop Sylvain Munaut from running Doom. The design uses a @1bitsquared iCEBreaker board with added SPI ram.

Watch:

Source: github.com/smunaut/doom_r…

@1bitsquared ⛵️Day 2: VexRiscv FPU

I've long wanted an FPGA-friendly #RISCV core with FPU. @SpinalHDL granted my wish this year by adding IEEE 754 support to VexRiscv. It now supports float and double with single-cycle FADD, FSUB, FMUL, and FMADD.

Source: github.com/SpinalHDL/VexR…

I've long wanted an FPGA-friendly #RISCV core with FPU. @SpinalHDL granted my wish this year by adding IEEE 754 support to VexRiscv. It now supports float and double with single-cycle FADD, FSUB, FMUL, and FMADD.

Source: github.com/SpinalHDL/VexR…

How much DooM can fit in a USB port? Quite a bit it turns out! A minuscule #Fomu #fpga board hosts my hardware/software re-implementation of the DooM render loop in the confines of a USB port (uses ~4200 LUTs and < 128 kB of internal RAM). (1/n)

This is a tiny piece of DooM in a 2.1x2.7 mm #fpga. That is pretty small! (can you see it below on the #Fomu board? you might have to zoom ...).

I created within a #riscv computer with specialized texturing and column drawing hardware. Designed to render DooM 1994 levels! (2/n)

I created within a #riscv computer with specialized texturing and column drawing hardware. Designed to render DooM 1994 levels! (2/n)

The OLED screen is connected to the #Fomu through jumper wires soldered on the pads (a trick inspired by @brunolevy01 Fomu vga mod). (3/n)

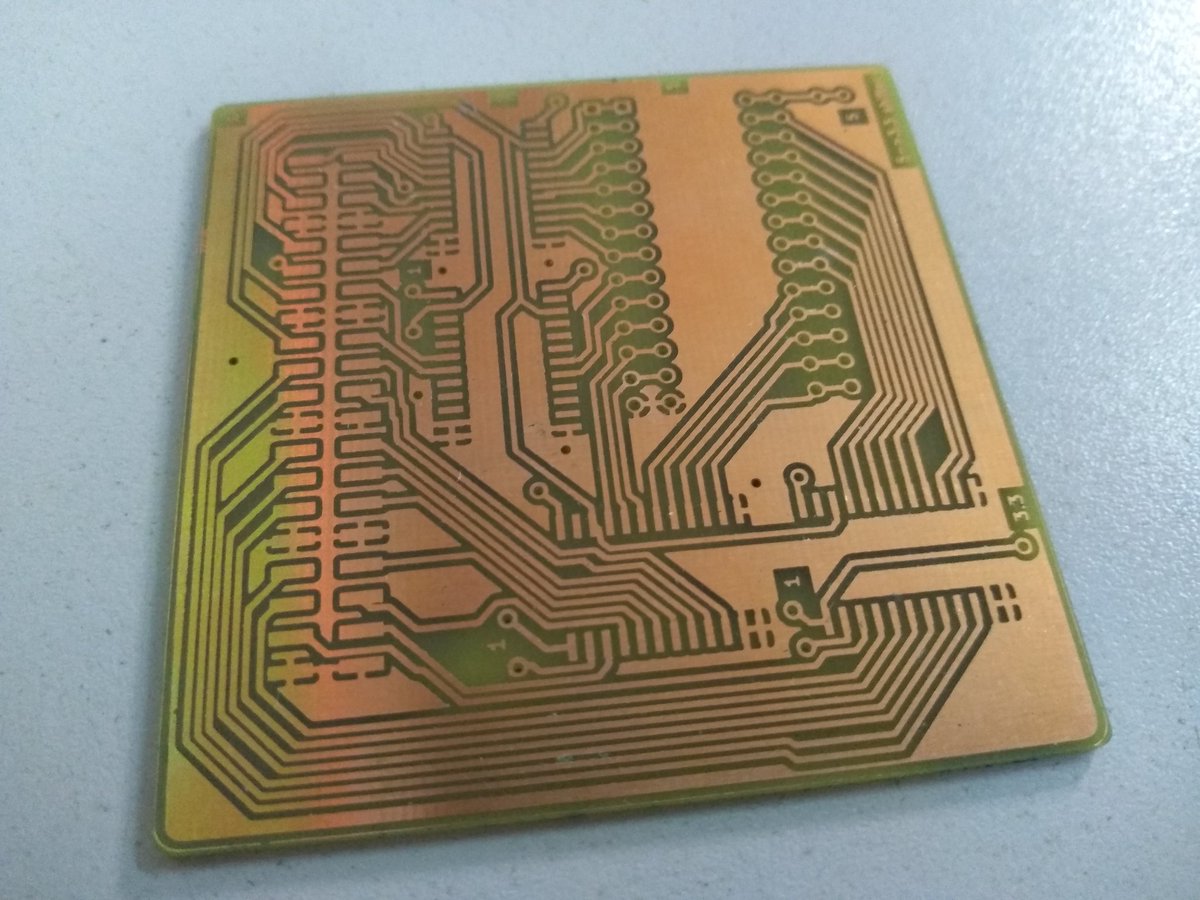

Please welcome a new addition to my collection of cheap #FPGA boards from eBay. This one is a PCIe variant of Pikes Peak accelerator from Microsoft. (1/8)

I have previously explored the Open CloudServer variant, in a special form factor and with a special motherboard connector. A longer description is available as a series of blog posts on my website: j-marjanovic.io (2/8)

PSX on FPGA, update #23:

Timer, Joystick and other things.

patreon.com/posts/41907082

#fpga #psx #MiSTerFPGA

Also, I am looking for verilog (or VHDL) dev willing to help me on the project. I think I really need support.

Please share the message, it is important.

Timer, Joystick and other things.

patreon.com/posts/41907082

#fpga #psx #MiSTerFPGA

Also, I am looking for verilog (or VHDL) dev willing to help me on the project. I think I really need support.

Please share the message, it is important.

I plan to share income from the Patreon, but only after milestones have been achieved (most of the people who helped me before did not deliver a single line of code after weeks (and in the end), I won't share in advance...)

I am looking for people interested in :

CPU:

- CPU integration (or remake)

- Integr. of GTE module into CPU.

- Integr. of Cache/Scratchpad into CPU.

Other:

- DMA / bus impl./ BIOS

- DDR debug

- CD Rom impl. (SW 90%)

- Dbug on FPGA board

- Integr. of other modules

PSX need YOU !

CPU:

- CPU integration (or remake)

- Integr. of GTE module into CPU.

- Integr. of Cache/Scratchpad into CPU.

Other:

- DMA / bus impl./ BIOS

- DDR debug

- CD Rom impl. (SW 90%)

- Dbug on FPGA board

- Integr. of other modules

PSX need YOU !

PSX on FPGA, update #16 :

GTE hardware implementation 86% complete.

Registers 100%, microcode 86%, data path and other mostly complete.

patreon.com/posts/39562211

#fpga #psx #MiSTerFPGA

GTE hardware implementation 86% complete.

Registers 100%, microcode 86%, data path and other mostly complete.

patreon.com/posts/39562211

#fpga #psx #MiSTerFPGA

PSX on FPGA, update #17 :

Now 95% done. RTPS / RTPT pass Amidog's test suite.

Remains :

- Only MVMVA instruction. (its two variants)

- Slow down instructions that takes less cycle than original timing.

- Faster DPCT (17 cycle instead of 18).

Now 95% done. RTPS / RTPT pass Amidog's test suite.

Remains :

- Only MVMVA instruction. (its two variants)

- Slow down instructions that takes less cycle than original timing.

- Faster DPCT (17 cycle instead of 18).

Hey everyone! I did a thing today. #FPGA Recall that tweet by @fpga_dave? Well, that day I ended up sending a message to @LatticeSemi via their web form. I didn't actually expect a reply. However, they DID.

1/

1/

And so I replied to that email, with a longer response expressing some of my thoughts of the state of the relationship with the open source community and an invitation to discuss in more detail. I didn't expect a reply there, either. But they DID.

2/

2/

@LatticeSemi invited me to a conference call with 3 of their senior execs. I accepted! As I don't think I'm qualified to be the spokesperson for the open source community, I arranged for @esden to join me on the call. He was of course his usual charismatic & informative self

3/

3/

--- PSX on FPGA ---

Update #11 : New post about PSX FPGA (Visible to everybody)

I think you'll like it.

patreon.com/posts/37038491

Stay safe.

Please like / RT for project awareness as usual.

#fpga #psx #MiSTerFPGA

Update #11 : New post about PSX FPGA (Visible to everybody)

I think you'll like it.

patreon.com/posts/37038491

Stay safe.

Please like / RT for project awareness as usual.

#fpga #psx #MiSTerFPGA

Seems I found my next bug !

(Sending GPU command from Avocado PSX emulator feeding my GPU)

(Sending GPU command from Avocado PSX emulator feeding my GPU)

Trying a GIF... :-)

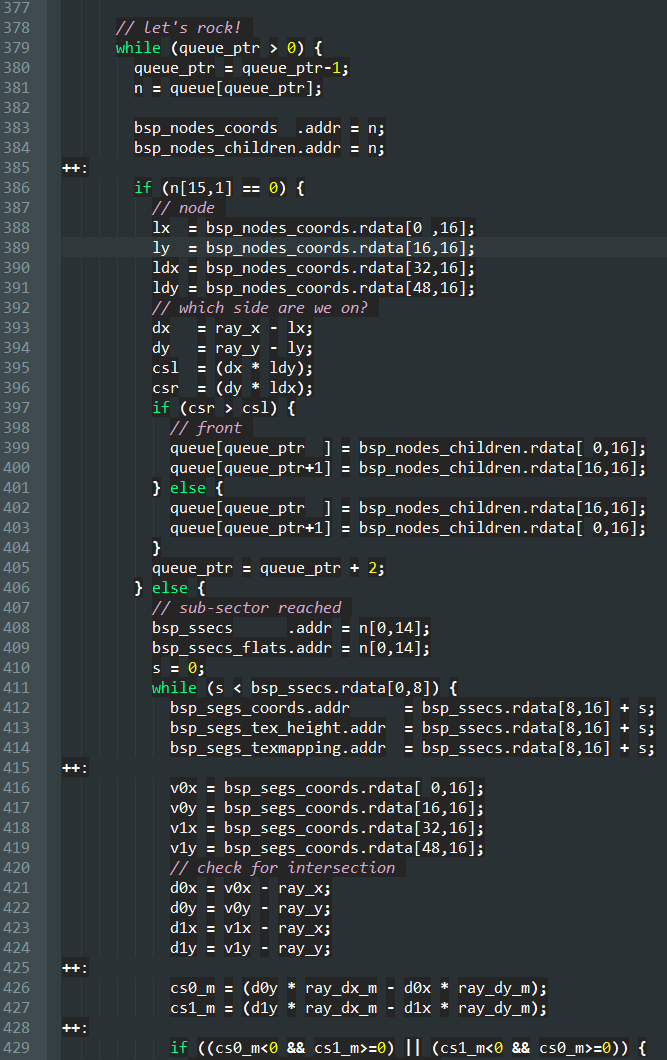

The DooM-chip! It will run E1M1 till the end of times (or till power runs out, whichever comes first).

Algorithm is burned into wires, LUTs and flip-flops on an #FPGA: no CPU, no opcodes, no instruction counter.

Running on Altera CycloneV + SDRAM. (1/n)

Algorithm is burned into wires, LUTs and flip-flops on an #FPGA: no CPU, no opcodes, no instruction counter.

Running on Altera CycloneV + SDRAM. (1/n)

Everything is described in a language I am working on: SDRAM controller, divider, BSP traversal, texture unit, etc.

Main renderer (w/o data) is 666 lines of code (!).

A great test case, made quite a few improvements, fixed some issues, learned a lot on CycloneV + Quartus.

(2/n)

Main renderer (w/o data) is 666 lines of code (!).

A great test case, made quite a few improvements, fixed some issues, learned a lot on CycloneV + Quartus.

(2/n)

Rendering uses the original BSP tree (of course!) but is modified to better fit a hardware implementation ; columns are raycast and drawn immediately front-to-back, stopping as soon as fully filled.

(3/n)

fabiensanglard.net/doomIphone/doo…

(3/n)

fabiensanglard.net/doomIphone/doo…

Wolfenstein 3D render loop in pure hardware! No CPU, no instruction pointer, no opcodes, only wires and flip-flops. Here runs on a Mojo V3 board (Xilinx Spartan 6) + SDRAM. Reading @fabynou black books while learning about #FPGA could only lead to this ;-)

(1/n)

(1/n)

Implemented from scratch using my language, from the SDRAM double-framebuffer to the Wolf3D DDA algorithm (and this is the original one; fixed point, DDA loop with only adds and shifts, tangent table!). 320x200, 256 18-bits colors palette and VGA output -- old school!

(2/n)

(2/n)

DDA algorithm heavily building on the original @ID_AA_Carmack AsmRefresh impl.:

github.com/id-Software/wo…

Fascinating to look back into it! Love these runtime patches ;-)

mov [BYTE cs:horizop],OP_JLE ; patch a jle in

(can't do on FPGAs ... unless reconfig at runtime ...??)

(3/n)

github.com/id-Software/wo…

Fascinating to look back into it! Love these runtime patches ;-)

mov [BYTE cs:horizop],OP_JLE ; patch a jle in

(can't do on FPGAs ... unless reconfig at runtime ...??)

(3/n)

Happy 25th birthday to the Playstation 1.

And happy birth to my patreon for the PSX FPGA Project :

patreon.com/laxer3a

Here is the appetizer...

#misterfpga #playstation1 #fpga

And happy birth to my patreon for the PSX FPGA Project :

patreon.com/laxer3a

Here is the appetizer...

#misterfpga #playstation1 #fpga

This is a simulation of the hardware GPU, each frame is 50 clock cycle. See my patreon post ;-)

Please RT like crazy :D :D :D

A BIG SUCCESS!

I've just found the right combination of #DisplayPort Transfer Unit (TU, aka "Packet Size") and Pixels per TU to allow standard 720p pixel clock down a single DP lane (and #FullHD down two lanes) - 40 bytes, with 11 pixel.

Life has become easy....

I've just found the right combination of #DisplayPort Transfer Unit (TU, aka "Packet Size") and Pixels per TU to allow standard 720p pixel clock down a single DP lane (and #FullHD down two lanes) - 40 bytes, with 11 pixel.

Life has become easy....

Sorry, just having a major #nerdgasm here.

I've been playing with #FPGA #DisplayPort and for a few years, and I have metaphorically found the keys to easy implementation of standard 720p & 1080p video while pulling weeds in the garden.

I've been playing with #FPGA #DisplayPort and for a few years, and I have metaphorically found the keys to easy implementation of standard 720p & 1080p video while pulling weeds in the garden.

Now I have a #FirstNerdProblem... work on this tonight or watch the @spacex launch?

Taking a couple of days off to see my pinball fanatic buddy Stuart in the UK. I want to make a pinball #fpga mashup! We're going to try and intercept ram writes and figure out when the high score is broken!

On the train to the airport I will test my verilog model of the SRAM against the real thing and see if I can read and write to it.

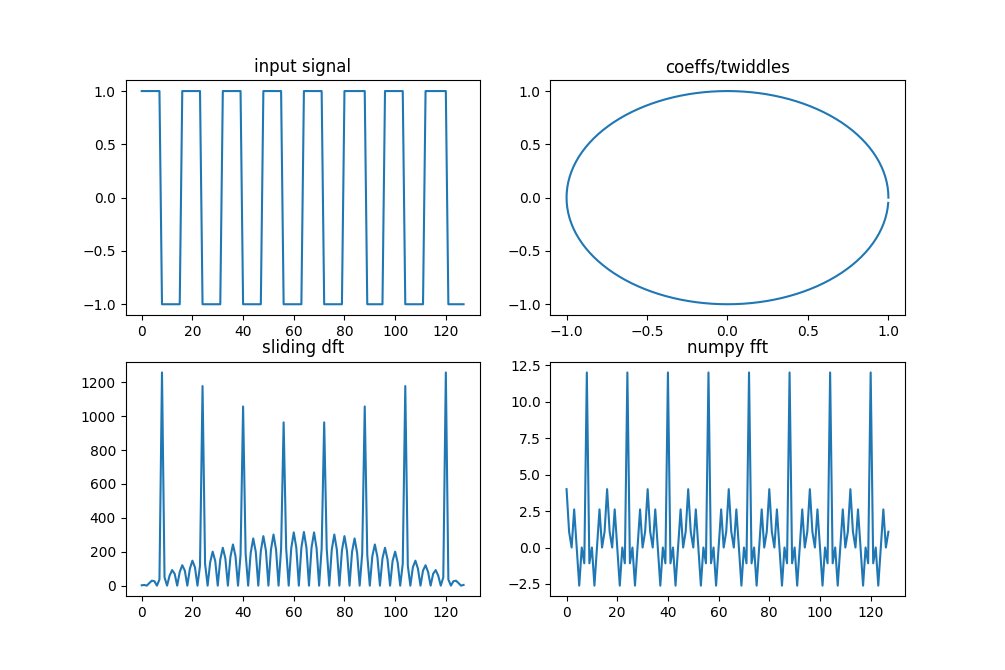

my next #fpga project as suggested by @ico_TC: Fourier analysis of fast ADC with results shown on a VGA monitor. This is such a cool video to understand what Fourier analysis is:

and this is a great paper on implementing the FFT in hardware - didn't think it was going to be so tricky! web.mit.edu/6.111/www/f201…

OK, @ebrombaugh gave me a tip on the sliding DFT comm.toronto.edu/~dimitris/ece4…

which looks a lot simpler to implement on an #FPGA. I've written the algo in python to test against the numpy FFT. github.com/mattvenn/fpga-…

which looks a lot simpler to implement on an #FPGA. I've written the algo in python to test against the numpy FFT. github.com/mattvenn/fpga-…

When activate IRQ on Zedboard with custom IRQ => Data Abort IRQ with Xilinx network code... Nice !!! #FPGA #HateShitLikeThat

Shit like that EVERYDAY !!! It gets REALLY TIRING !!!

So my code is fucked. IRQ broken.

Breaking news !!!

Now custom chipset tested with sample asset & loader...

#fpga #2D #demoscene #oldschool

Still bug decoded in comments...

Now custom chipset tested with sample asset & loader...

#fpga #2D #demoscene #oldschool

Still bug decoded in comments...

- Image not stable... Was stable before. WTF.

- DDR clock to verify (pixel and not bus ?!)

- Priority of 2D over CPU...

- DDR clock to verify (pixel and not bus ?!)

- Priority of 2D over CPU...

Time to sleep... near 3 AM. Science says that brain will start to eat itself if no sleep...